## A Novel MMIC Approach to Sampling Phase/Frequency Detection for Microwave Quartz-Lock Oscillators

Tadao Nakagawa, Tetsuo Hirota and Takashi Ohira

NTT Radio Communication Systems Laboratories, Yokosuka, Japan

**Abstract** - A novel concept in sampling phase/frequency detection for microwave quartz-lock oscillators is proposed, and its prototype is developed in a GaAs MMIC. It is found out experimentally that the proposed detector provides drastic improvement over conventional sampling phase detectors in pull-in range.

### I. INTRODUCTION

The sampling phase detector (SPD) is one of the key devices for quartz locking of microwave oscillators [1]-[4]. It unfortunately has an inherent disadvantage that the pull-in range of phase locked oscillators (PLOs) using SPDs is narrow because SPDs have phase sensitivity but no frequency sensitivity. To recover the locked condition when the loop becomes unlocked, a search circuit is necessary in the SPD PLOs. However, the sweep frequency range of a search circuit is severely confined because it could possibly lock onto an unwanted adjacent harmonic of the reference frequency. A potential alternative is the direct division type PLO, which uses frequency dividers and is usually combined with a phase frequency

comparator (PFC) [5]-[7]. However, the direct division type has relatively high phase noise and high subharmonic spurs due to the frequency dividers.

This paper proposes a novel circuit for sampling phase/frequency detection. It can detect both frequency and phase without any frequency dividers. The frequency comparison output can extend the pull-in range to the limit, which is equal to the reference frequency. We call this circuit the "sampling phase frequency comparator (SPFC)". The first trial of the SPFC integration on an MMIC chip is also described, with successful performances measured in the Ku-band frequencies.

### II. PRINCIPLES

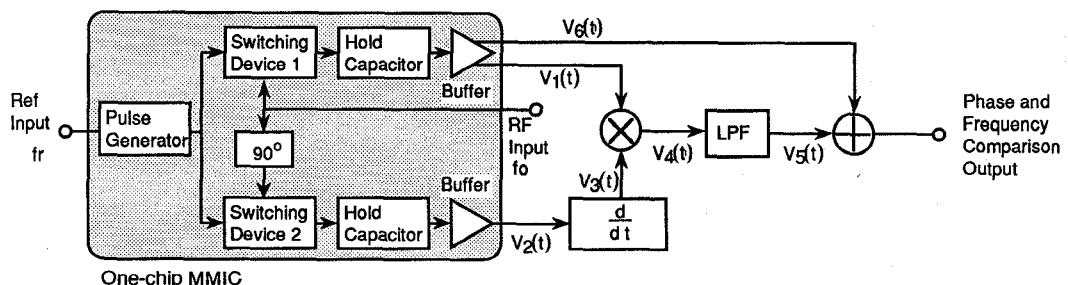

The proposed SPFC configuration is shown in Fig. 1. The pulse generator creates narrow-width pulses synchronized to the reference crystal oscillator. The RF input is directly sampled by the narrow-width pulses at Switching Device 1 and the RF input through the  $90^\circ$  phase shifter is sampled by the same narrow-width pulses at Switching Device 2.

Fig.1 Configuration of sampling phase frequency comparator

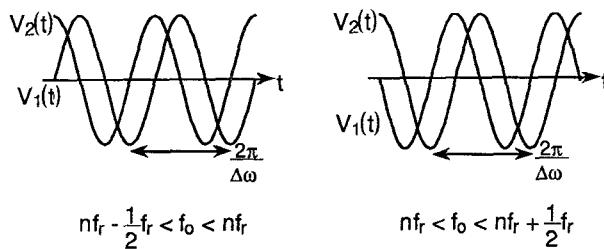

Outputs  $V_1(t)$  and  $V_2(t)$  are obtained on the hold capacitors. The frequency of both outputs is equal to the difference between the RF frequency  $f_o$  and the harmonic of the reference frequency  $f_r$ . The relationship between  $V_1(t)$  and  $V_2(t)$  when  $f_o$  is less than the harmonic of  $f_r$  is different from that when  $f_o$  is greater than the harmonic of  $f_r$  as shown in Fig. 2.  $V_1(t)$  leads  $V_2(t)$  by  $90^\circ$  if

$$nf_r - \frac{1}{2}f_r < f_o < nf_r \quad (1)$$

and  $V_1(t)$  lags  $V_2(t)$  by  $90^\circ$  if

$$nf_r < f_o < nf_r + \frac{1}{2}f_r \quad (2)$$

where  $n$  is the harmonic number. Therefore, when  $f_o$  is less than  $nf_r$ , we may write the following expression for the output wave forms of  $V_1(t)$  and  $V_2(t)$ :

$$V_1(t) = \sin\Delta\omega t \quad (3)$$

$$V_2(t) = \cos\Delta\omega t \quad (4)$$

where  $\Delta\omega$  is the frequency difference between  $f_o$  and  $nf_r$ . The differential circuit output of  $V_3(t)$  is given by

$$V_3(t) = \frac{d}{dt}(V_2(t)) \\ = -\Delta\omega\sin\Delta\omega t \quad (5)$$

and the multiplier output of  $V_4(t)$  by

$$V_4(t) = V_1(t) \times V_3(t) \\ = -\Delta\omega\sin^2\Delta\omega t \\ = -\frac{\Delta\omega(1 - \cos2\Delta\omega t)}{2} \quad (6)$$

Fig. 2 Phase relationship between outputs  $V_1(t)$  and  $V_2(t)$

This shows that  $V_4(t)$  consists of DC component  $-1/2\Delta\omega$  and an AC component, the frequency of which is  $2\Delta\omega$ .

On the other hand, when  $f_o$  is greater than  $nf_r$ , the outputs are

$$V_1(t) = -\sin\Delta\omega t \quad (7)$$

$$V_2(t) = \cos\Delta\omega t \quad (8)$$

and

$$V_3(t) = \frac{d}{dt}(V_2(t)) \\ = -\Delta\omega\sin\Delta\omega t. \quad (9)$$

Consequently,

$$V_4(t) = V_1(t) \times V_3(t) \\ = \Delta\omega\sin^2\Delta\omega t \\ = \frac{\Delta\omega(1 - \cos2\Delta\omega t)}{2} \quad (10)$$

By comparing Eqn. (6) with Eqn. (10), we find the polarity of the DC component of  $V_4(t)$  is when  $f_o$  is less than  $nf_r$  is the opposite of that when  $f_o$  is greater than  $nf_r$ . Therefore, by implementing the SPFC in the PLO, the DC signal  $V_5(t)$  obtained at the LPF will pull the VCO frequency toward the harmonic. If  $f_o$  is within the pull-in range around  $nf_r$ , the phase lock will be achieved by the phase detection signal  $V_6(t)$  and the frequency comparison signal  $V_4(t)$  will become zero because  $\Delta\omega$  is zero.

### III. MMIC FABRICATION

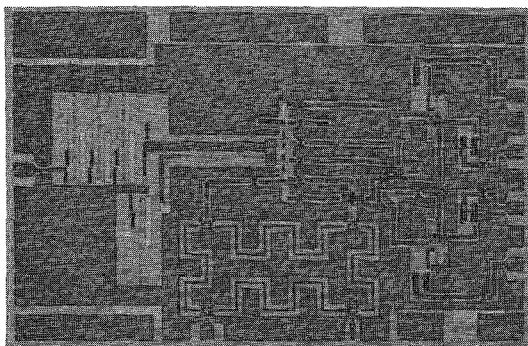

The circuits of the pulse generator, switching devices and hold capacitors are based on our previously-reported MMIC SPD up to 20 GHz [4]. The pulse generator consists of limiters, a delay inverter and a NOR-gate. The switching devices are transfer gate FETs. The design of these circuits was simulated on SPICE. The optimization goal was to obtain the maximum amplitude of the beat signal which was generated when the RF frequency was not a multiple of the reference frequency. To combine the pulse generator, the switching FETs and hold capacitors with an 11 GHz reduced-size

branch-line 90° hybrid [8] and buffer amplifiers, the MMIC SPFC was integrated on a 3.0 mm × 2.0 mm GaAs monolithic chip as shown in Fig. 3.

#### IV. EXPERIMENTAL RESULTS

##### Frequency Comparator Operation

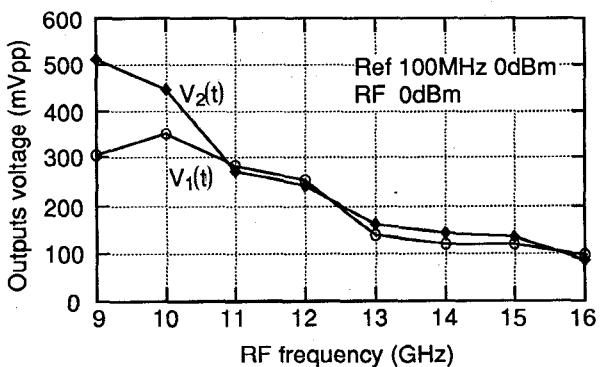

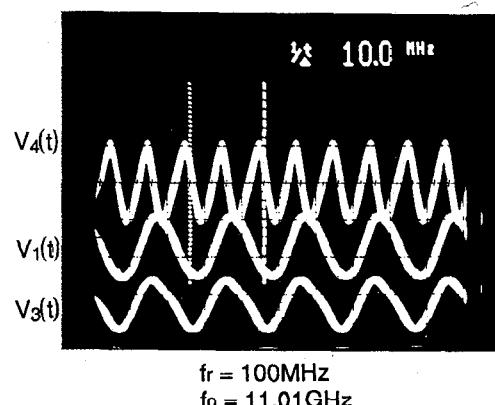

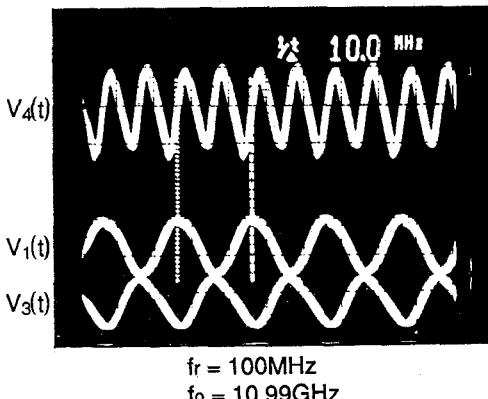

Fig. 4 shows the measured outputs  $V_1(t)$  and  $V_2(t)$  as functions of the RF input frequency. The difference between  $V_1(t)$  and  $V_2(t)$  in frequency dependence is due to the branch-line hybrid. Outputs of more than 100 mVpp in the Ku-band were obtained with a 100MHz-0dBm reference signal.

The frequency was compared, and the comparison results are shown in Fig. 5. The symbols in this figure correspond to those in Fig. 1. The reference input was 100 MHz and the RF input was 10 MHz higher and lower than 11 GHz. It was found that  $V_4(t)$  has an AC

Fig. 3 Photograph of the MMIC SPFC

Chip size: 3.0 mm × 2.0 mm

Fig. 4 Outputs  $V_1(t)$  and  $V_2(t)$  of MMIC SPFC

component, the frequency of which is 20 MHz, and a DC component which indicates whether the RF frequency is above or below the multiple of the reference frequency.

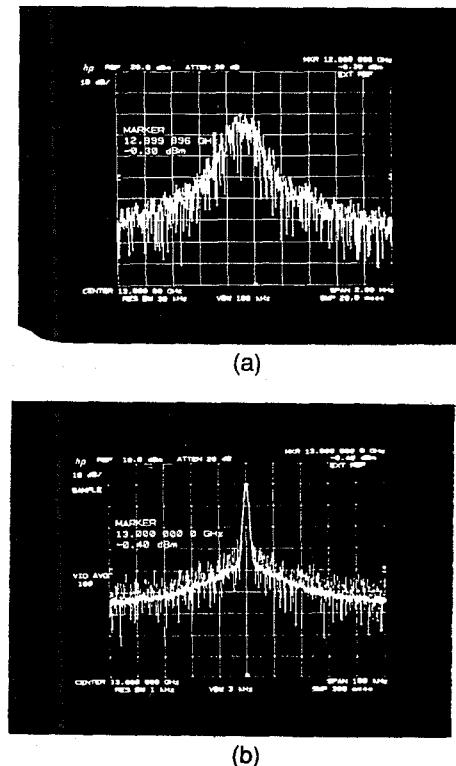

##### Application to Ku-band PLO

The SPFC was applied to a Ku-band PLO. An MMIC VCO with a frequency range of 11.6-13.7 GHz [7] was employed in the PLO. The reference input was 100 MHz. Fig. 6(a) shows the spectrum when only the frequency comparison output was put into the VCO. Fig. 6(b) shows the spectrum when the phase detection output was also put into the VCO. It was found that the frequency comparison output pulled the VCO frequency around the harmonic of the reference frequency and by adding the phase detection output, the phase lock was achieved. The little deviation from the harmonic in Fig. 6(a) is probably due to the DC offset of the multiplier.

Fig. 5 Frequency comparator operation

A pull-in range of 100 MHz was achieved in this PLO, while that in conventional SPD PLOs is only about 10 MHz. Consequently, no search circuits are necessary in this PLO.

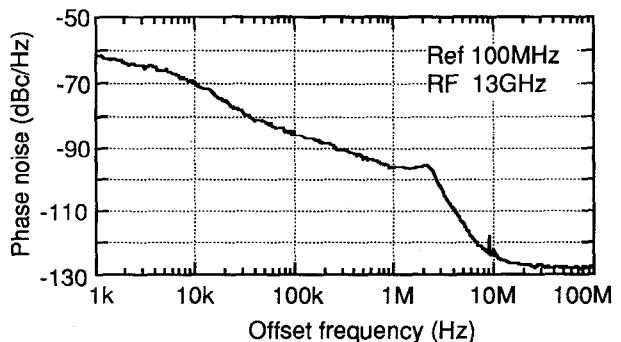

The measured phase noise performance in the locked condition is shown in Fig. 7. The phase noise was below -70 dBc/Hz at 10 kHz off from the carrier. No spurs were found throughout the DC up to the 20 GHz frequency range.

## V. CONCLUSION

A novel phase detector which we call SPFC is proposed. It can detect both frequency and phase without any frequency dividers. A GaAs MMIC SPFC has been newly developed and applied to a Ku-band PLO. The pull-in range was extended to about 10 times that of conventional approaches. It will hopefully be a key device in a variety of frequency-stabilized and low phase

Fig. 6 Output spectrum of MMIC SPFC PLO

(a) frequency comparison alone

Center: 13GHz, H: 200kHz/div, V: 10dB/div

(b) phase and frequency comparison.

Center: 13GHz, H: 10kHz/div, V: 10dB/div

noise microwave oscillators.

## ACKNOWLEDGMENT

The authors would like to thank Dr. H. Yamamoto, K. Morita and Dr. M. Aikawa for their stimulating encouragement. They also wish to thank S. Saito and H. Ichino for their participation in helpful discussions.

## REFERENCES

- [1] A. Milano et al, "Low noise high stability, X-band frequency generator for on board satellite equipment", Proc. Eur. Microwave Conf., vol. 16, pp. 827-832, 1986.

- [2] W. G. Varlin et al, "High-performance digital radio uses state-of-the-art thin-film technology", Microwave Syst. News, vol. 17, no.6, pp.8-20, June 1987.

- [3] J. Andrews et al, "GaAs MMIC phase locked source", IEEE MTT-S Int. Microwave Symp. Dig., pp. 815-818, 1989.

- [4] T. Nakagawa et al, "GaAs MMIC sampling phase detector for phase-locked oscillators up to 20GHz", 3rd APMC Proc., pp.1121-1123, 1990.

- [5] M. Takahashi et al, "A 9.5 GHz Commercially available 1/4 GaAs dynamic prescaler with suppressed noise performance," IEEE Microwave and Millimeter-Wave Monolithic Circuits Symp. Dig., pp. 31-35, 1988.

- [6] J. Archer et al, "Development and Evaluation of a GaAs MMIC phase-locked loop chip set for space applications," IEEE Trans. Microwave Theory Tech., vol. MTT-37, no. 4, pp. 790-792, 1989.

- [7] T. Ohira et al, "Dual-chip GaAs monolithic integration Ku-band phase locked loop microwave synthesizer," IEEE Trans. Microwave Theory Tech., vol. MTT-38, no. 9, pp. 1204-1209, 1990.

- [8] T. Hirota et al, "Reduced-Size branch-line and rat-race hybrids for uniplanar MMIC's", IEEE Trans. Microwave Theory Tech., vol. MTT-38, no. 3, pp. 270-275, 1990.

Fig. 7 SSB phase noise of the developed MMIC SPFC PLO